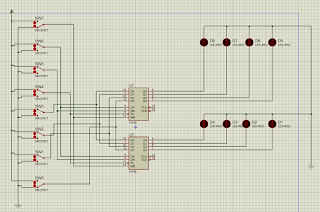

Synchronous Binary Counter

1. Switch SPDT

2. Ground

3. Power

4. IC 74193

5. IC

6. LED

S0 : Switch Reset

S1 : Switch Up

S2 : Switch Down

S3 : Switch Load

Pada rangkaian

percobaan 3 A ini terdapat 2 IC yaitu 74192 dan 74193 yang pada masing-masing

memiliki counter yang berbeda. Pada IC 74192 dapat melakukan dari 0 – 9

sedangkan pada IC 74193 dapat melakukan counter dari 0-15 . Pada setiap pin

pada masing- masing IC dihubungkan dengan switch spdt.

Pada rangkaian IC

74192 untuk dapat mengaktifkan counter, nilai pin 11(load) harus pada kondisi

HIGH(1) atau tidak diaktifkan (aktif low) dan pin 14 (Reset) harus pada kondisi

LOW(0). Untuk melakukan counter up, input pada pin UP harus mendapatkan nilai clock

negative edge atau saat low (1 ke 0) sehingga akan terjadi counter up pada

outputnya 0-9

Untuk melakukan

counter down, maka input pada pin DOWN harus mendapatkan nilai clock negative

edge atau saat low (1 ke 0). Maka S2 harus dilakukan clock dengan mengaktifkan

lalu tidak mengaktifkan switch sehingga terjadi counter down mulai dari 9-0.

Pada rangkaian IC

74193 untuk dapat mengaktifkan counter, nilai pin 11(load) harus pada kondisi

HIGH(1) dan pin 14 (Reset) harus pada kondisi LOW(0). Untuk melakukan counter

up, input pada pin UP harus mendapatkan nilai clock negative edge atau saat low

(1 ke 0) sehingga akan terjadi counter up pada outputnya 0-15

Untuk melakukan

counter down, maka input pada pin DOWN harus mendapatkan nilai clock negative

edge atau saat low (1 ke 0). Maka S2 harus dilakukan clock dengan mengaktifkan

lalu tidak mengaktifkan switch sehingga terjadi counter down mulai dari 15-0.

Untuk mereset ulang

nilai baik itu saat Up/Down maka S0 di logika high, dan jika S3 (load) low maka

nilai output akan tergantung D0, D1, D2, D3 apakah dia high atau low

Percobaan 3 A

1. Analisa

output yang dihasilkan berdasarkan IC yang digunakan

· IC

74193

Berdasarkan percobaan yang dilakukan pada

switch 0 yang berupa reset jika berlogika high maka semua output akan berlogika

low dan mengulang counter. Jika pada IC 74193 pada kaki input up/down tidak

diberi clock maka output akan berlogika low, dan akan berlogika high tergantung

pada kaki D0, D1, D2, dan D3 apakah berlogika high/low saat input load diberi

berlogika low.

Jika pada kaki input up/down diberi clock

dan reset berlogika 0 maka akan terjadi counter, jika kaki up yang diberi clock

maka akan mengcounter up sampai bilangan 15, sedangkan jika kaki down diberi

clock maka akan counter down mulai dari bilangan 15.

· IC

74192

Berdasarkan percobaan yang dilakukan pada

switch 0 yang berupa reset jika berlogika high maka semua output akan berlogika

low dan mengulang counter. Jika pada kaki input up/down tidak diberi clock maka

output akan berlogika low, dan akan berlogika high tergantung pada kaki D0, D1,

D2, dan D3 apakah berlogika high/low saat input load diberi logika low.

Jika pada kaki input up/down diberi clock

dan reset berlogika 0 maka akan terjadi counter, jika kaki up yang diberi clock

maka akan mengcounter up sampai bilangan 9, sedangkan jika kaki down diberi

clock maka akan counter down mulai dari bilangan 9.

2. Jika

switch 3 dan 4 off analisa IC 74 output yang dihasilkan

Jika input kaki down dan load off maka hasil output

tergantung dari nilai input D0, D1, D2, dan D3, hal ini karena load yang

merupakan aktif low saat diberi berlogika low maka akan aktif, jika kaki up

maupun down diberi clock tidak akan mengubah outputnya, karena output hanya

tergantung dari nilai input D0, D1, D2, dan D3.

Tidak ada komentar:

Posting Komentar